جمعه, ۲۴ اسفند, ۱۴۰۳ / 14 March, 2025

مجله ویستا

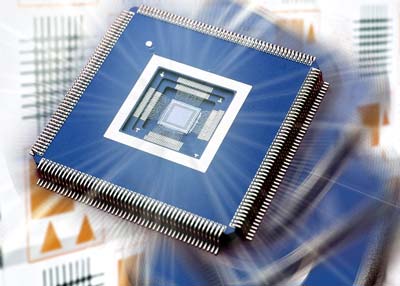

سوپرکامپیوتر بر روی یک چیپ

Doug Burger، یک استاد علوم کامپیوتر در دانشگاه تگزاس، میگوید مشکلی که در این مورد وجود دارد این است که برای آنکه نرمافزارهای کاربردی از این هستههای چندگانه بهره ببرند، برنامهنویسان باید کدهای خود را برای پردازش موازی سازماندهی نمایند، و این امر در مورد برخی برنامهها دشوار یا غیر ممکن است.او میگوید: "صنعت در حال حرکت به سوی یک مانع برنامهنویسی است، مسئولیت را بر دوش نرمافزار میگذارد و انتظار دارد که برنامهنویس بتواند کدهایی را برای سیستمهای آنها بنویسد." Burger و همکارانش امیدوارند این مسائل را به کمک یک معماری جدید ریزپردازنده و مجموعه دستورالمعل بنام Trips (Tera-op Reliable Intelligently Adaptive Processing System) حل نمایند. او میگوید: "هدف ما انجام اعمال پردازشی به صورت همزمان است، چه این امکان از سوی برنامهنویس برای شما فراهم گردد و چه از راهی غیر از این باشد".

Trips از تکنیکهای متعددی برای محقق نمودن این امر استفاده میکند. اول، کامپایلر Trips کد قابل اجرا را در بلاکهایی که حداکثر حاوی ۱۲۸ دستورالعمل هستند به سختافزار میفرستد. پردازنده کل یک بلاک را یکباره در نظر میگیرد و اجرا مینماید، انگار که آن یک دستورالعمل واحد است، که این امر به میزان قابل توجهی باعث کاهش سربار ناشی از اداره و زمانبندی دستورالعمل میگردد.

دوم، به جای این که ترتیب اجرا از سوی کامپایلر یا برنامهنویس تعیین گردد، دستورالعملهای درون یک بلاک به صورت "جریان داده" اجرا میشوند، به این معنی که هر دستورالعمل به محض اینکه ورودیهای آن وارد گردیدند اجرا میشود. Steve Keckler، یک استاد علوم کامپیوتر و یکی از همکاران ارشد Burger در پروژه Trips، میگوید: "داده خود در میان دستورالعملها جریان مییابد."

● افزایش کارآیی

یک ترفند دیگر: درون یک بلاک، کامپایلر Trips میتواند دو دستورالعمل را که در دو مسیر مختلف قرار دارند در صورتی که مقصد و عملیات آنها یکسان باشد درون یک دستورالعمل واحد ادغام نماید. پروفسور Kathryn McKinley، که بخش کامپایلر پروژه Trips را راهبری مینماید، میگوید: "مدل جریان داده ما در مقایسه با طراحیهای قبلی مبتنی بر مفاهیم جریان داده، این فرصت را در اختیار کامپایلر قرار میدهد که کد کارآتر و کارآمدتری را تولید نماید." در نهایت، اجرای جریان داده دارای ویژگی "رمزنگاری مستقیم مقصد" است که باعث میشود نتایج یک دستورالعمل مستقیما به دستورالعمل مصرفکننده بعدی برود بدون اینکه موقتا در یک فایل رجیستر مرکزی ذخیره گردد. این ویژگی سربار پردازش را بیش از پیش کاهش میدهد و سرعت محاسبه را افزایش میدهد. و در مقایسه با روشهای سنتی بهبود کارآیی – افزایش سرعت کلاک پردازنده و ساخت pipeline های عمیقتر – بهبودهای ایجاد شده در کارآیی از سوی این تکنیکها به قیمت یک افزایش اندک در توان مصرفی حاصل میگردند.

چالش مواجهه با مصرف توان، سازندگان چیپ را وادار به حرکت به سوی چیپهای چند هستهای مینماید. Mark McDermott که قبلا مهندس شرکت اینتل بوده و در حال حاضر قائممقام مدیرعامل Coherent Logix است میگوید: "شما به چیزی همچون Pentium دقت کنید، در آنجا حجم عظیمی از منطق کنترل وجود دارد، ترانزیستورهای کنترلی که هیچ کاری انجام نمیدهند – آنها صرفا انرژی مصرف مینمایند. Trips در حال تلاش برای منتقل ساختن بخشی از این پیچیدگی به کامپایلر است". او میگوید: "جایی که Trips در آن واقعا خواهد درخشید، کارآیی بسیار بسیار بالای محاسبهگری تعبیه شدهی جریان داده است، همچون SDR (software-defined radio)". اما، McDermott میافزاید، "من هنوز نمیدانم آیا آن یک اکسیر معجزهآسا است یا خیر. هنوز تحقیقات بیشتری باید صورت گیرد." بر طبق اعلام توسعهدهندگان این پروژه، تکنیکهای جریان داده Trips با سه نوع همزمانی ایجاد شده در نرمافزار به خوبی کار میکنند – موازیگری سطح دستورالعمل، سطح thread و سطح داده. به همین دلیل، Trips به عنوان polymorphous شناخته میشود، به این معنی که آن میتواند بر روی انواع بسیار متفاوتی از برنامههای کاربردی به خوبی عمل نماید – علمی، تجاری و تعبیه شده.

و این دقیقا همان کیفیتی است که از سوی آژانس پروژههای تحقیقاتی پیشرفته دفاعی (Defense Advanced Research Projects Agency) در پروژه معماریهای محاسبهگری Polymorphous (Polymorphous Computing Architectures) دنبال میشود. DARPA، که با پرداخت مبلغ ۱۵/۴ میلیون دلار در حال همکاری با پروژه Trips است، به دنبال چیپی است که بر روی بسیاری از برنامههای کاربردی قادر به انجام یک تریلیون عملیات (tera-op) در هر ثانیه باشد. دانشگاه در صدد تحویل طرح Trips خود به IBM است، که نمونه اولیه چیپها را خواهد ساخت و در ماه فوریه به دانشگاه تحویل خواهد داد. این چیپها دارای دو هسته پردازنده خواهند بود، که هر کدام قادر به اجرای ۱۶ دستورالعمل همزمان هستند.بنا بر گفته Keckler، چیپها که با سرعت ۵۰۰ مگاهرتز کار میکنند ۱۶ میلیارد عملیات را در هر ثانیه انجام خواهند داد. او میگوید، دانشگاه برای تجاری شدن این تکنولوژی به صنعت چشم خواهد دوخت و هدف DARPA را که عرضه چیپهای ۱۰ گیگاهرتزی با توانایی ۱ tera-op است تا سال ۲۰۱۲ محقق خواهد نمود.

Burger میگوید: "ما علاقهی زیادی به تجاریسازی این تکنولوژی داریم، و به دنبال شرکای تجاری هستیم". دسترسپذیری تجاری وسیع چیزی است که DARPA نیز به دنبال آن است. آن با ویژگی polymorphism خود این امکان را برای پنتاگون فراهم میسازد که به جای خریداری پردازندههای سفارشی برای سیستمهای خاص اقدام به خریداری چیپهای ارزان قیمت نماید. Chuck Moore، یکی از کارکنان ارشد شرکت Advanced Micro Devices، میگوید Trips وعدههای فراوانی داده است. او میگوید: "ایدهها به خوبی با رفتار واقعی کد سازگار هستند. جنبههای polymorphous تکنولوژی Trips میتواند آن را قادر به انجام کار موفقیتآمیز بر روی انواع متفاوت و گستردهای از برنامهها و محاسبهگریها نماید". از نظر Moore، یکی از بزرگترین چالشهای پیش روی تبدیل شدن به یک پردازنده تجاری عمده، سازگاری با نرمافزارها و سیستمهای موجود است، به خصوص سازگاری x۸۶. او میگوید، اما یک راه برای حفظ سازگاری استفاده از Trips به عنوان کمک-پردازنده (co-processor) است. "پردازنده همه منظوره x۸۶ میتواند "کارهای سنگین را به کمک-پردازنده محول نماید ضمن این که سازگاری با نسل قبل را بر روی خود حفظ مینماید".

Moore خاطرنشان میکند که علیرغم وعده تکنولوژی Trips، در سطح بازار، معرفی و ارائه چیزهای کاملا جدید کار دشواری است. این گونه به نظر میرسد که آن باید از یک موقعیت خاص شروع کند و در آنجا مزایای خود را نشان دهد. هنگامی که آن توانست مفید بودن خود را در بخشهای کلیدی بازار به اثبات برساند، به احتمال قریب به یقین میتواند به شکلی وسیعتر گسترش یابد.

نویسنده: Gary H. Anthes

مترجم: امین ایزدپناه

منبع : علم الکترونیک و کامپیوتر

ایران مسعود پزشکیان دولت چهاردهم پزشکیان مجلس شورای اسلامی محمدرضا عارف دولت مجلس کابینه دولت چهاردهم اسماعیل هنیه کابینه پزشکیان محمدجواد ظریف

پیاده روی اربعین تهران عراق پلیس تصادف هواشناسی شهرداری تهران سرقت بازنشستگان قتل آموزش و پرورش دستگیری

ایران خودرو خودرو وام قیمت طلا قیمت دلار قیمت خودرو بانک مرکزی برق بازار خودرو بورس بازار سرمایه قیمت سکه

میراث فرهنگی میدان آزادی سینما رهبر انقلاب بیتا فرهی وزارت فرهنگ و ارشاد اسلامی سینمای ایران تلویزیون کتاب تئاتر موسیقی

وزارت علوم تحقیقات و فناوری آزمون

رژیم صهیونیستی غزه روسیه حماس آمریکا فلسطین جنگ غزه اوکراین حزب الله لبنان دونالد ترامپ طوفان الاقصی ترکیه

پرسپولیس فوتبال ذوب آهن لیگ برتر استقلال لیگ برتر ایران المپیک المپیک 2024 پاریس رئال مادرید لیگ برتر فوتبال ایران مهدی تاج باشگاه پرسپولیس

هوش مصنوعی فناوری سامسونگ ایلان ماسک گوگل تلگرام گوشی ستار هاشمی مریخ روزنامه

فشار خون آلزایمر رژیم غذایی مغز دیابت چاقی افسردگی سلامت پوست